Carsten R.

Foriker

- Beiträge

- 86

- Ort

- Halle (Saale)

Mahlzeit zusammen und allen hier noch ein gesundes neues Jahr.

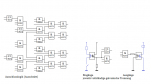

Für die Umsetzung einer Ausschlusslogik mittels CMOS-Schaltkreisen benötige ich mangels eigener Erfahrung mal etwas Hilfe. Was ich prinzipiell vorhabe, sollte die beigefügte Skizze erkennen lassen. Versorgung erfolgt mit 12V=. Das Ganze soll auf Rasterplatinen (die mit den 3er-Gruppen) unter Verwendung von Stecksockeln montiert werden, elektrische Verbindungen mittels Draht (Ätzerei kommt nicht in Frage). Der Ausschnitt zeigt etwa ein Viertel der gesamten Logik, das wird auf einer Platine nicht unterzubringen sein.

Und nun meine Fragen:

1. In welcher Größenordnung liegt die Längenbegrenzung (durch den Leitungswiderstand) zwischen Ausgang eines Gatters und dem Eingang des nachfolgenden? Dass ich diese Abstände kurz zu halten versuche, versteht sich von selbst. Aber wenn ich von einer Platine zur nächsten muss, könnten es schon mal bis zu 30 cm werden.

2. Muss man auf Mindestabstände oder Abschirmung gegenüber anderen Stromkreisen besonders achten?

3. Ist es erforderlich, die Eingänge zu entprellen? Hierzu sei angemerkt, dass an den Eingängen eher statische Zustände (Lage von Weichen und Relais) und Tastenbedienungen erfasst werden, also keine schnellen Schaltfolgen. Es gab vor längerer Zeit schon einmal eine Diskussion über das Entprellen der Eingänge. Da wurde einerseits argumentiert, dass unter den vorliegenden und mit meinen vergleichbaren Voraussetzungen das Entprellen entbehrlich sei. Diese Argumentation war für mich nachvollziehbar. Aber einer der Diskussionsteilnehmer behauptete (allerdings nur mit dem Argument seiner Erfahrung), man müsse immer entprellen, sonst könne das unerwünschte Effekte haben. Was könnte also schiefgehen, wenn man hier auf das Entprellen verzichtet???

4. Welche Vorsichtsmaßnahmen sind beim Umgang mit den ICs wegen deren elektrostatischer Empfindlichkeit wirklich angebracht? Dazu habe ich recht gegensätzliche Auffassungen gelesen. Reicht eine Berührung der vollständig verdrahteten und bestückten Platine tatsächlich aus, um die ICs abzuschießen?

5. Welche Optokoppler (nach Möglichkeit aus dem Sortiment von Reichelt) sind für die Ein- und Ausgänge geeignet? Mir fällt es schwer, in den Datenblättern das zu finden, was mich wirklich interessiert: den minimalen Strom auf der Eingangsseite, um den Ausgang in die Sättigung zu bringen.

6. Gibt es bei den Logik-Gattern ein typisches Ausfallverhalten? Äußert sich ein defektes UND-Gatter z. B. eher dadurch, dass der Ausgang auf HIGH geht, obwohl nicht alle Eingänge HIGH sind? Oder eher so, dass trotz aller Eingänge auf HIGH der Ausgang LOW bleibt? Oder muss man gar damit rechnen, dass bei defektem Gatter am Ausgang überhaupt nichts mehr ist? Letzteres würde bei Kaskadierung (diese ist beabsichtigt) eine Art Kettenreaktion hervorrufen, oder?

7. Wäre es zur Vermeidung einer solchen Kettenreaktion sinnvoll, alle Gatter-Ausgänge, welche auf den Eingang eines weiteren Gatters führen, hochohmig (wie hoch?) mit Masse zu verbinden?

Vielen Dank schon im Voraus für alle hilfreichen Antworten,

schönes Restwochenende und beste Grüße

Carsten

Für die Umsetzung einer Ausschlusslogik mittels CMOS-Schaltkreisen benötige ich mangels eigener Erfahrung mal etwas Hilfe. Was ich prinzipiell vorhabe, sollte die beigefügte Skizze erkennen lassen. Versorgung erfolgt mit 12V=. Das Ganze soll auf Rasterplatinen (die mit den 3er-Gruppen) unter Verwendung von Stecksockeln montiert werden, elektrische Verbindungen mittels Draht (Ätzerei kommt nicht in Frage). Der Ausschnitt zeigt etwa ein Viertel der gesamten Logik, das wird auf einer Platine nicht unterzubringen sein.

Und nun meine Fragen:

1. In welcher Größenordnung liegt die Längenbegrenzung (durch den Leitungswiderstand) zwischen Ausgang eines Gatters und dem Eingang des nachfolgenden? Dass ich diese Abstände kurz zu halten versuche, versteht sich von selbst. Aber wenn ich von einer Platine zur nächsten muss, könnten es schon mal bis zu 30 cm werden.

2. Muss man auf Mindestabstände oder Abschirmung gegenüber anderen Stromkreisen besonders achten?

3. Ist es erforderlich, die Eingänge zu entprellen? Hierzu sei angemerkt, dass an den Eingängen eher statische Zustände (Lage von Weichen und Relais) und Tastenbedienungen erfasst werden, also keine schnellen Schaltfolgen. Es gab vor längerer Zeit schon einmal eine Diskussion über das Entprellen der Eingänge. Da wurde einerseits argumentiert, dass unter den vorliegenden und mit meinen vergleichbaren Voraussetzungen das Entprellen entbehrlich sei. Diese Argumentation war für mich nachvollziehbar. Aber einer der Diskussionsteilnehmer behauptete (allerdings nur mit dem Argument seiner Erfahrung), man müsse immer entprellen, sonst könne das unerwünschte Effekte haben. Was könnte also schiefgehen, wenn man hier auf das Entprellen verzichtet???

4. Welche Vorsichtsmaßnahmen sind beim Umgang mit den ICs wegen deren elektrostatischer Empfindlichkeit wirklich angebracht? Dazu habe ich recht gegensätzliche Auffassungen gelesen. Reicht eine Berührung der vollständig verdrahteten und bestückten Platine tatsächlich aus, um die ICs abzuschießen?

5. Welche Optokoppler (nach Möglichkeit aus dem Sortiment von Reichelt) sind für die Ein- und Ausgänge geeignet? Mir fällt es schwer, in den Datenblättern das zu finden, was mich wirklich interessiert: den minimalen Strom auf der Eingangsseite, um den Ausgang in die Sättigung zu bringen.

6. Gibt es bei den Logik-Gattern ein typisches Ausfallverhalten? Äußert sich ein defektes UND-Gatter z. B. eher dadurch, dass der Ausgang auf HIGH geht, obwohl nicht alle Eingänge HIGH sind? Oder eher so, dass trotz aller Eingänge auf HIGH der Ausgang LOW bleibt? Oder muss man gar damit rechnen, dass bei defektem Gatter am Ausgang überhaupt nichts mehr ist? Letzteres würde bei Kaskadierung (diese ist beabsichtigt) eine Art Kettenreaktion hervorrufen, oder?

7. Wäre es zur Vermeidung einer solchen Kettenreaktion sinnvoll, alle Gatter-Ausgänge, welche auf den Eingang eines weiteren Gatters führen, hochohmig (wie hoch?) mit Masse zu verbinden?

Vielen Dank schon im Voraus für alle hilfreichen Antworten,

schönes Restwochenende und beste Grüße

Carsten